# Универсальный цифровой модуль приемника с возможностью анализа входного сигнала до 2 ГГц. *С.В.Логвиненко. ПРАО АКЦ ФИАН*

#### Основные черты модуля:

- ✓ Максимальная частота оцифровки 1 ГГц

- ✓ Возможность анализа входного сигнала до 2 ГГц

- ✓ Максимальная полоса анализа 500 МГц

- ✓ Встроенный синтезатор частоты с низким уровнем джиттера

- ✓ Возможность использования для синхронизации внешних сигналов

- ✓ Обмен данными с компьютером универсальная шина РСІ 33МГц

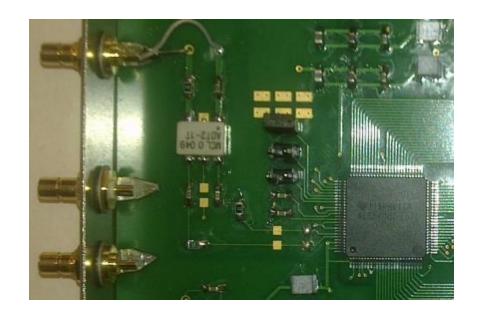

### Внешний вид платы. Размер 150х95мм.

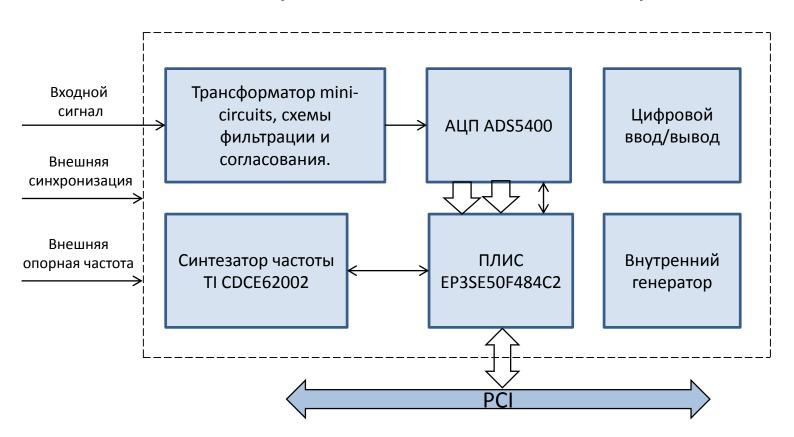

### Функциональная схема модуля

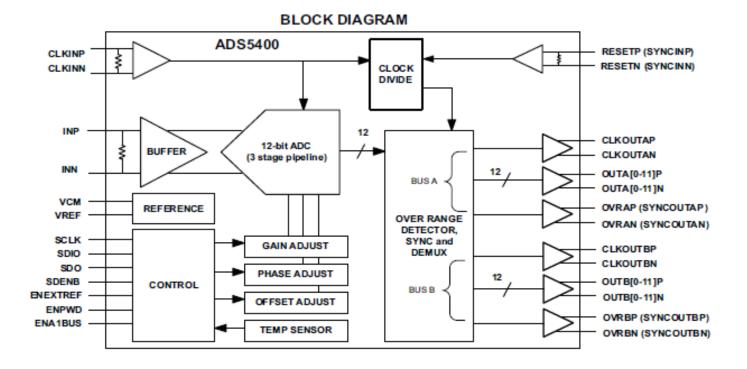

### **АЦП TI ADS5400**

### Основные параметры:

- ✓ On-Chip Analog Buffer

- √ 1-GSPS Sample Rate

- **√** 100-Pin TQFP PowerPAD™ Package

- √ 12-Bit Resolution (16-mm × 16-mm Footprint With Leads)

- ✓ 2.1 GHz Input Bandwidth

- ✓ Industrial Temperature Range = -40°C to 85°C

- ✓ SFDR = 66 dBc at 1.2 GHz APPLICATIONS

- ✓ SNR = 57.6 dBFS at 1.2 GHz

- Максимальная скорость оцифровки 1ГГц.

- Для передачи данных в ПЛИС можно использовать режим передачи по одной или двум шинам. Тактовая частота передачи равна Fsample/2 или Fsample/4. При максимальной частоте оцифровки 1ГГц это 500 или 250МГц.

- Для управления режимами работы используется SPI интерфейс.

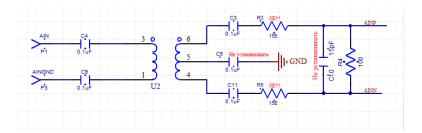

• Возможность выбора трансформатора, установка фильтра, выбор согласования.

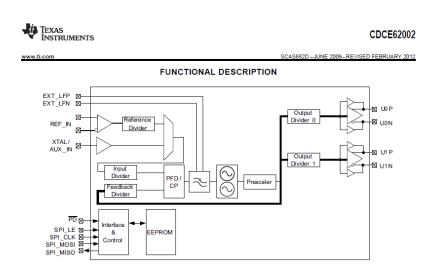

### Синтезатор частоты TI CDCE62002.

- 0.5 ps RMS (10 kHz to 20 MHz) Output Jitter

Performance

- Low Output Phase Noise: -130 dBc/Hz at 1MHz offset, Fc = 491.52 MHz

- Output Frequency Ranges From 10.94 MHz

to 1.175 GHz in Synthesizer Mode

- LVPECL, LVDS and LVCMOS

- Independent Output Dividers Support

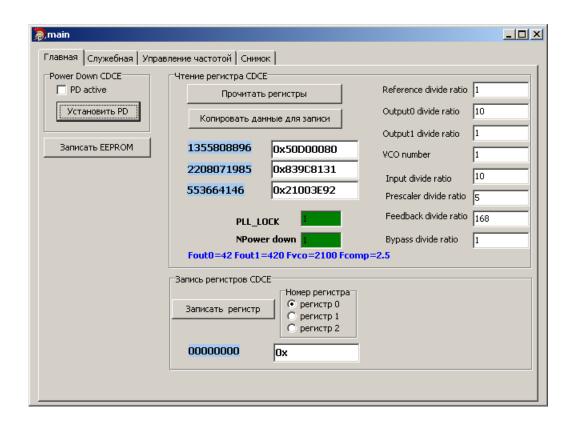

## Управление синтезатором от компьютера через SPI (Serial Peripheral Interface).

#### ПЛИС Altera EP3SE50484F

Table 1-21 lists the Stratix III DSP block performance specifications.

Table 1-21. DSP Block Performance Specifications for Stratix III Devices (Note 1)

| Mode                                                             | Number of<br>Multipliers | <b>C2</b> (5)            | C3                       | C4                       | C4 C4L                   |                          | 13                          | 14                         | I4L                         |      |

|------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|-----------------------------|----------------------------|-----------------------------|------|

|                                                                  |                          | V <sub>ccl</sub> = 1.1 V | V <sub>ccl</sub> = 1.1 V | V <sub>cc.</sub> = 1.1 V | V <sub>cc.</sub> = 1.1 V | V <sub>ccl</sub> = 0.9 V | V <sub>cct</sub> =<br>1.1 V | V <sub>cc.=</sub><br>1.1 V | V <sub>ccl</sub> =<br>0.9 V | Unit |

| 9×9-bit multiplier (a, c, e, g) (2)                              | 1                        | 440                      | 365                      | 315                      | 315                      | 240                      | 345                         | 315                        | 225                         | MHz  |

| 9×9-bit multiplier (b, d, f, h) (2)                              | 1                        | 500                      | 410                      | 375                      | 375                      | 270                      | 385                         | 375                        | 250                         | MHz  |

| 12×12-bit multiplier (a, e) (3)                                  | 1                        | 440                      | 365                      | 315                      | 315                      | 240                      | 345                         | 315                        | 225                         | MHz  |

| 12×12-bit multiplier (b, d, f, h) (3)                            | 1                        | 500                      | 410                      | 375                      | 375                      | 270                      | 385                         | 375                        | 250                         | MHz  |

| 18×18-bit multiplier                                             | 1                        | 600                      | 495                      | 440                      | 440                      | 320                      | 470                         | 440                        | 300                         | MHz  |

| 36×36-bit multiplier                                             | 1                        | 440                      | 365                      | 315                      | 315                      | 220                      | 345                         | 315                        | 205                         | MHz  |

| Double mode                                                      | 1                        | 440                      | 365                      | 315                      | 315                      | 220                      | 345                         | 315                        | 205                         | MHz  |

| 18×18-bit multiply adder                                         | 2                        | 490                      | 405                      | 345                      | 345                      | 250                      | 380                         | 345                        | 235                         | MHz  |

| 18×18-bit multiply adder                                         | 4                        | 490                      | 405                      | 345                      | 345                      | 250                      | 380                         | 345                        | 235                         | MHz  |

| 18×18-bit multiply adder with loop<br>back                       | 2                        | 490                      | 405                      | 345                      | 345                      | 250                      | 380                         | 345                        | 235                         | MHz  |

| 18×18-bit multiply adder with loop back (4)                      | 2                        | 390                      | 320                      | 300                      | 240                      | 180                      | 300                         | 300                        | 135                         | MHz  |

| 18×18-bit multiply accumulator                                   | 4                        | 475                      | 390                      | 330                      | 330                      | 240                      | 370                         | 330                        | 225                         | MHz  |

| 18×18-bit multiply adder with chainout                           | 4                        | 475                      | 390                      | 330                      | 330                      | 240                      | 370                         | 330                        | 225                         | MHz  |

| Input Cascade Independent output<br>of four 18×18 bit multiplier | 4                        | 550                      | 455                      | 415                      | 415                      | 270                      | 430                         | 415                        | 250                         | MHz  |

| 36-bit shift (32 bit data)                                       | 1                        | 475                      | 390                      | 330                      | 330                      | 250                      | 370                         | 330                        | 235                         | MHz  |

Table 1-9. Performance with the Streaming Data Flow Engine Architecture—Stratix III Devices

| Points | Combinational<br>ALUTs | Logic<br>Registers | Memory<br>(Bits) | Memory<br>(M9K) | 18 × 18<br>Blocks | f <sub>MAX</sub><br>(MHz) | Clock<br>Cycle<br>Count | Transform<br>Time (µs) |

|--------|------------------------|--------------------|------------------|-----------------|-------------------|---------------------------|-------------------------|------------------------|

| 256    | 2,141                  | 3,688              | 39,168           | 20              | 12                | 397                       | 256                     | 0.64                   |

| 1,024  | 2,434                  | 4,383              | 155,904          | 20              | 12                | 406                       | 1,024                   | 2.52                   |

| 4,096  | 3,732                  | 5,929              | 622,848          | 76              | 24                | 361                       | 4,096                   | 11.35                  |

Table 1–10 shows the variable streaming data flow performance, with in order inputs and bit-reversed outputs, for width 16 (32 for floating point), for Stratix III (EP3SE50F780C2) devices.

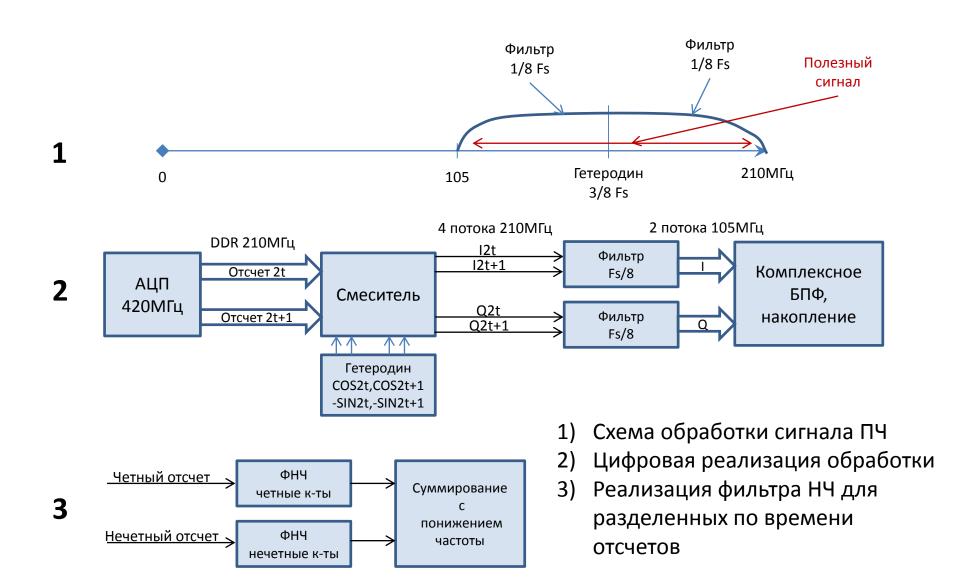

### Регистрация сигнала ПЧ для пульсарных наблюдений.

### Анализатор спектра с полосой 500МГц.

# Спасибо за внимание!